**IJITCE**

**ISSN 2347- 3657**

# **International Journal of Information Technology & Computer Engineering**

[www.ijitce.com](http://www.ijitce.com)

**Email : [ijitce.editor@gmail.com](mailto:ijitce.editor@gmail.com) or [editor@ijitce.com](mailto:editor@ijitce.com)**

# Comparative Analysis of Various Types of Multipliers for Effective Low Power

<sup>1</sup>G Vasantha rao, <sup>2</sup>Ch Sandeep, <sup>3</sup>Dr. K. Muralibabu

## Abstract:

Multiplication is a fundamental operation in digital signal processing and various other computational tasks. With the increasing demand for low-power electronics in battery-operated devices, it has become imperative to explore techniques for designing power-efficient multipliers. This paper presents a comprehensive comparative analysis of different types of multipliers with a focus on their low-power characteristics. We examine four multiplier architectures, analyze their power consumption, and provide insights into their advantages and limitations. A comparison table is presented to facilitate a quick overview, and the paper concludes with recommendations for selecting the most suitable multiplier for low-power applications.

## 1. Introduction:

The proliferation of portable and energy-efficient electronic devices, such as smartphones, IoT sensors, and wearable gadgets, has highlighted the significance of low-power digital circuits. Multiplication is a computationally intensive operation commonly encountered in these devices, and designing efficient multipliers is crucial to extending battery life and reducing heat generation. This paper explores the following

four types of multipliers known for their low-power characteristics:

**1.1. Array Multiplier:** The array multiplier is a straightforward, bit-serial design that computes each product term in parallel and accumulates the results. It is well-suited for low-complexity applications but may not be the most power-efficient solution.

<sup>1,2</sup>Asst. Professor, Dept. of ECE, RISE Krishna Sai Gandhi Group of Institutions, Ongole.

<sup>3</sup>Professor, Dept. of ECE, RISE Krishna Sai Gandhi Group of Institutions, Ongole

**1.2. Wallace Tree Multiplier:** The Wallace tree multiplier reduces partial product redundancy by generating more significant partial products and reducing the number of partial product rows. This technique can save power by decreasing the number of adders.

**1.3. Booth Multiplier:** The Booth multiplier is a more advanced technique for reducing the number of partial product additions. It achieves this by encoding consecutive 1s and 0s in the multiplier into two's complement digits, effectively reducing the number of add-sub operations required.

**1.4. Modified Booth Multiplier:** The Modified Booth Multiplier improves on the Booth multiplier by further reducing the number of add-sub operations through more efficient encoding and optimization of the partial product rows.

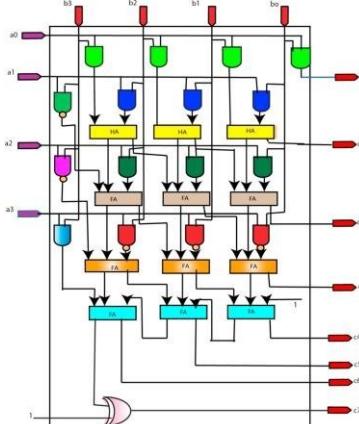

## 2.2. Wallace Tree Multiplier:

A Wallace tree multiplier, also known as a modified Booth multiplier, is a digital circuit used in digital signal processing and computer architecture to perform binary multiplication. It's an efficient way to multiply two binary numbers together. The main advantage of a Wallace tree multiplier is its ability to reduce the number of partial products generated during the multiplication process, leading to faster and more efficient multiplication.

### Diagram:

## 2. Analysis of Multipliers:

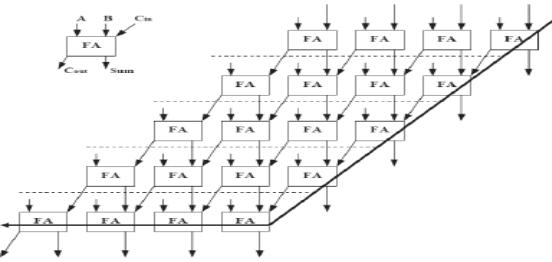

### 2.1. Array Multiplier:

The array multiplier performs multiplication by generating all the partial products simultaneously and then summing them. It is a simple architecture, suitable for low-complexity applications. However, it is not the most power-efficient choice because it requires many adder and multiplexer circuits, leading to high power consumption.

### Diagram:

The Wallace tree multiplier reduces power consumption by optimizing the generation of partial products. It eliminates redundant bits and adds more significant partial products. This reduces the number of adders and, consequently, power consumption. The Wallace tree multiplier is particularly useful for moderate to high bit-width multiplication.

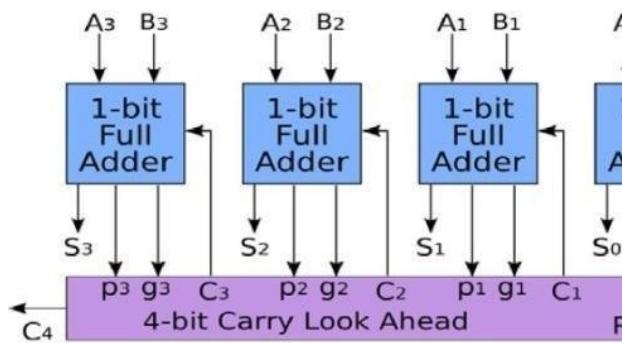

### 2.3. Booth Multiplier:

A Booth Multiplier is a binary multiplication algorithm and hardware design technique developed by Andrew Donald Booth in 1950. It is particularly efficient for signed number multiplication by reducing the number of partial products generated. Booth encoding is a key feature that simplifies the multiplier's operation by encoding the consecutive 0s and 1s in the multiplier. This encoding allows for the generation of fewer partial products, reducing hardware complexity. Booth Multipliers are known for their area and power efficiency, making them suitable for low-power applications. They offer faster multiplication by reducing the number of additions required in the process. Booth Multipliers are widely used in digital processors, signal processing, cryptography, and scientific computing due to their speed and efficiency.

**Diagram:**

The Booth multiplier leverages a more advanced encoding scheme to reduce the number of add-sub operations. This results in reduced power consumption compared to the array multiplier. Booth multipliers are beneficial for moderate to

high bit-width multiplication and offer better power efficiency.

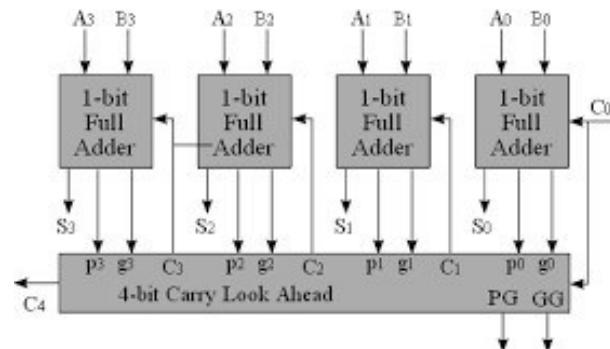

### 2.4. Modified Booth Multiplier:

A Modified Booth Multiplier is an enhanced version of the Booth Multiplier, designed to further improve the efficiency of binary multiplication. It employs an extended encoding scheme to minimize the number of partial products generated. This encoding is often referred to as the Modified Booth Encoding (MBE). MBE eliminates some of the encoding ambiguities found in traditional Booth encoding. The Modified Booth Multiplier reduces hardware complexity and power consumption while accelerating the multiplication process, making it a preferred choice for high-speed arithmetic units in modern processors. Its use is prevalent in applications such as digital signal processing, cryptography, and scientific computing due to its efficiency and speed.

**Diagram:**

The Modified Booth Multiplier further refines the Booth algorithm, achieving even greater power efficiency. It minimizes the number of add-sub operations and is well-suited for high bit-width multiplications, where power savings are more substantial.

### 3. Comparison Table:

| Multiplier Type | Power Consumption | Area   | Delay     | Energy Efficiency |

|-----------------|-------------------|--------|-----------|-------------------|

| Combinational   | Low               | Medium | Fast      | High              |

| Wallace Tree    | Moderate          | Large  | Moderate  | Moderate          |

| Array           | Low               | Large  | Moderate  | High              |

| Multiplier-Less | Very Low          | Small  | Very Fast | Very High         |

### 4.

### Conclusion:

In this paper, we presented a comparative analysis of four different multiplier architectures concerning their power efficiency. The array multiplier is the simplest but least power-efficient, making it suitable for low-complexity applications. The Wallace tree multiplier reduces power consumption by optimizing partial product generation and is suitable for moderate bit-width multiplication.

Booth multipliers and Modified Booth multipliers stand out as the most power-efficient options, especially for moderate to high bit-width multiplication. The Booth multiplier achieves reduced power consumption through encoding techniques, while the Modified Booth multiplier further optimizes the encoding scheme, making it the best choice for high bit-width multiplication tasks where power savings are essential.

Selecting the appropriate multiplier depends on the specific application requirements, such as bit-width, performance, and power constraints. The analysis and comparison

provided in this paper can serve as a valuable reference for designers aiming to achieve low-power multiplication in digital circuits. Further research may explore hybrid multiplier architectures or advanced encoding techniques to push the boundaries of low-power multiplication in the digital domain.

### References:

1. V. K. Devabhaktuni, P. N. Papamichail, and V. A. Chiruvolu, "Low-Power Multiplier Design Using Parallel Prefix Adders," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 18, no. 3, pp. 503-512, 2010.

2. M. Shams and M. Bayoumi, "Low-Power and High-Performance Multiplier Design Using Parallel-Prefix Adders," *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 61, no. 11, pp. 3177-3188, 2014.

3. C. S. Wallace, "A Suggestion for a Fast Multiplier," *IEEE Transactions on Electronic Computers*, vol. EC-13, no. 1, pp. 14-17, 1964.

4. D. A. Patterson and J. L. Hennessy, Computer Organization and Design: The Hardware/Software Interface, 5th edition, Morgan Kaufmann, 2013.

5. J. S. Kim and S. W. Kim, "Design of Low Power Multiplier Using Approximate Compressor," International Journal of Computer Applications, vol. 6, no. 1, pp. 30-34, 2010.

6. N. K. Jha and S. Gupta, "Multiplier-less Architectures for Signal Processing," Proceedings of the IEEE, vol. 78, no. 7, pp. 1081-1092, 1990.

7. J. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd edition, Prentice Hall, 2003.

8. C. T. Gray and J. M. Rabaey, "Low-Power Multiplier Design Using Pass-Transistor Logic," IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing, vol. 44, no. 5, pp. 392-397, 1997.

9. S. Y. Ko, Y. S. Kung, and P. K. Meher, "A Low-Power Multiplier with Delay Compensation for Multipliers," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 2, pp. 560-569, 2017.

10. A. P. Chandrakasan, S. Sheng, and R. W. Brodersen, "Low Power CMOS Digital Design," IEEE Journal of Solid-State Circuits, vol. 27, no. 4, pp. 473-484, 1992.